Instruction Set (ISA)

- 서로 다른 컴퓨터들(CPU)은 서로 다른 명령어 집합을 가지고 있다.

- ARM ISA - RISK : 명령어 수가 적고, 사이클 수를 적게 가져감.

- X86 ISA - CISK : 명령어 수가 많고, 사이클 수도 다양함.

- 많은 부분에서 공통점을 가지고 있다.

- 초창기의 컴퓨터들은 매우 단순한 명령어 집합을 가지고 있었음

- 컴퓨터의 구현을 간단하게 만들 수 있었지만, 단순한 명령어를 여러번 사용해야 했음

- 현대의 많은 컴퓨터들도 비교적 단순한 명령어 집합을 택하고 있다.

ARMv8 Instruction Set

- 앞으로의 예제들에 사용할 ARMv8의 부분 집합을 "LEGv8"이라고 하자...!

- ARMv8은 다양한 분야에서 응용되고 있다.

- 전자제품

- 네트워크 및 저장 장치

- 카메라, 프린터...

- 현대의 많은 ISA들의 전형적인 형태로 볼 수 있다.

Arithmetic Operation

- 덧셈과 뺄셈은 세 개의 피연산자를 사용한다.

- 두 개의 소스(입력)와 하나의 목적지(출력)을 가진다.

- 예) ADD(SUB) a, b, c -> a에 b+c의 결과가 저장됨.

- 모든 산술 연산은 위의 형태를 가지고 있음

디자인 원칙 1. Simplicity favours Regularity; 단순성은 규칙성을 선호한다.

- 규칙성은 구현을 더 간단하게 해줌

- 단순성은 더 높은 성능을 더 낮은 비용으로 달성할 수 있게 해줌.

Arithmetic Example

- C code

- f = ( g + h ) - ( i + j );

- Complied code

- ADD t0, g, h // temp t0 = g + h

- ADD t1, i, j // temp t1 = i + j

- SUB f, t0, t1 // f = t0 - t1

Register Operands

- 산술 명령어는 "레지스터 피연산자"를 사용한다.

- LEGv8은 64비트의 레지스터가 32개 있다.

- 자주 접근하는 데이터를 저장하는데 사용된다.

- 64비트의 데이터는 "doubleword"라고 불린다.

- X0 ~ X30의 범용 레지스터가 있고 X31의 특수한 목적의 레지스터가 있다.

- 32비트의 데이터는 "word"라고 불린다.

- W0 ~ W30의 범용 서브 레지스터가 있고, W31의 특수한 목적의 서브 레지스터가 있다.

디자인 원칙 2. Smaller is Faster; 작을수록 빠르다.

메인 메모리와 대조되는 점. 메인 메모리는 수백만 개의 저장 위치를 가지지만, 접근 속도가 상대적으로 느리다.

LEGv8 Registers

- X0 ~ X7 : 함수 호출 시 인자 전달 및 반환 값 저장

- 함수 호출 시 인자들은 일반적으로 X0부터 순서대로 전달됨.

- X8 : 간접적인 반환 값 위치 지정

- 함수의 반환값이 커서 하나의 레지스터에 담을 수 없는 경우, X8에 반환 값이 저장될 메모리 주소를 지정

- X9 - X15 : 임시 레지스터

- 함수 내부에서 임시적인 계산 결과를 저장하는 데 사용

- X16 ~ X17 (IP0 - IP1) : 링커 스크래치 레지스터 또는 임시 레지스터

- 링커가 사용하거나 함수 내부에서 임시적으로 사용되는 레지스터

- X18 : 플랫폼 레지스터 또는 임시 레지스터

- 플랫폼에 따라 특정한 용도로 사용되거나, 임시 레지스터로 사용됨.

- X19 ~ X27 : 저장 레지스터

- 함수 호출 시 값을 보존해야 하는 레지스터

- 함수를 호출하기 전에 이 레지스터들의 값을 스택에 저장하고, 함수 호출 후 복원

- X28(SP) : 스택 포인터

- 스택의 가장 위쪽을 가리키는 포인터.

- 함수 호출 시 지역변수나 저장된 레지스터 값을 스택에 할당하고 해제하는데 사용

- X29(FP) : 프레임 포인터

- 현재 함수의 스택 프레임의 시작 부분을 가리키는 포인터.

- 지역 변수나 인자에 접근하는데 사용

- X30(LR) : 링크 레지스터

- 함수 호출 후 복귀할 주소를 저장.

- 함수가 끝나면 LR에 저장된 주소로 이동하여 프로그램을 계속 실행

- XZR(register 31) : 상수 0

- 항상 0의 값을 가지는 레지스터이다.

- 변수 초기화나 연산등 특수한 용도로 사용한다.

Register Operand Example

- C code

- f = ( g + h ) - ( i + j ) ;

- f, g, h, i , j 변수는 각각 X19, X20, X21, X22, X23에 할당

- Assembly Code

- ADD X9, X20, X21

ADD X10, X22, X23

SUB X19, X9, X10

- ADD X9, X20, X21

** Memory Operands 추가하기 **

Immediate Operands

- Immediate Operands는 명령어에 포함된 상수값을 의미한다.

- ex) ADDI X22, X22, #4 -> 여기서 #4는 실제 상수값 4를 의미한다.

- 이러한 명령어가 필요한 이유? -> 자주 사용되니깐.

디지인 원칙 3. Make the Common case fast; 일반적인 경우를 빠르게 하자

작은 상수들은 프로그래밍에서 자주 사용된다.

Immediate Operands를 사용하면 레지스터에 값을 저장하고 불러오는 것을 피해 성능을 높일 수 있다.

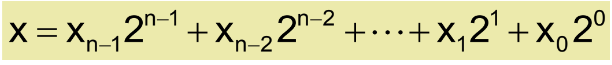

Unsigned Binary Integers

- n-bit의 숫자가 주어진다 했을 때

- 0 ~ 2^n - 1 의 값을 표현할 수 있다.

- 32-bit의 경우에는 0에서 4,294,967,295까지의 값을 표현할 수 있다.

- Example

- 0000 0000 0000 0000 0000 0000 0000 1011_(2)

- = 0 + ... + 1x2^3 + 0x2^2 + 1x2^1 + 1x2^0

- = 0 + 8 + 0 + 2 + 1 = 11_(10)

2's Complement Signed Integers

- n-bit의 숫자가 주어진다 했을 때

- -2^(n-1) 에서 2^(n-1) - 1의 값을 표현할 수 있다.

- 32비트의 경우에는 -2,147,483,648 에서 2,147,483,647까지의 값을 표현할 수 있다.

- Example

- 1111 1111 1111 1111 1111 1111 1111 1100_(2)

- = -1x2^31 + 1x2^30 + ... + 1x2^2 + 0x2^1 + 0x2^0

- = -2,147,483,648 + 2,147,483,644 = -4_(10)

- 가장 왼쪽 비트(31번째 비트)는 부호 비트이다.

- 부호 비트가 1이면 음수를

- 부호 비트가 0이면 0과 양수를 나타낸다.

- 가장 큰 음수 : 1000 0000 ... 0000

- 가장 작은 음수 : 1111 1111 .... 1111

- 가장 큰 양수 : 0111 1111 .... 1111

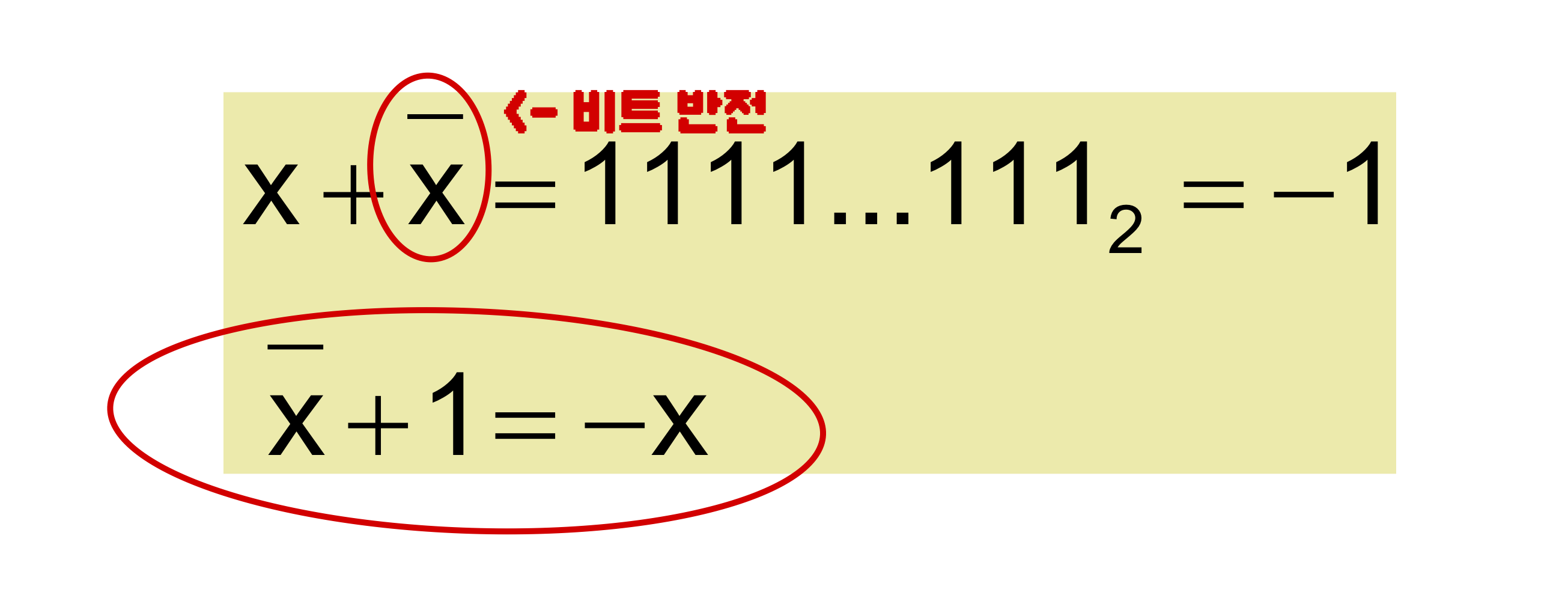

Signed Negation

- 부호를 바꾸는 방법 : 비트 반전 후 1 더하기

- 비트 반전 : 1 -> 0, 0 -> 1

- Example

- +2 = 0000 0000 ... 0010

- -2 = 1111 1111 ... 1101 + 1

= 1111 1111 ... 1110

Sign Extension

- 부호 확장은 숫자를 더 많은 비트를 사용해서 나타내는 방법을 의미한다.

- 숫자 값은 유지한채 비트의 수를 늘린다.

- 부호 확장은 부호 비트를 왼쪽으로 복사하는 방법으로 이루어진다.

- Example 8-bit -> 16-bit

- +2 = 0000 0010 -> 0000 0000 0000 0010

- -2 = 1111 1110 -> 1111 1111 1111 1110

- 해당 기능을 하는 명령어

- LDURSB : Sign-Extend loaded byte

- LDURB : zero-extend loaded byte

Representing Instructions

- 명령어들은 바이너리로 인코딩 되어있으며, "machine code"라고 불린다.

- LEGv8 명령어

- 32비트 명령어 단어로 인코딩 됨

- 연산코드(opcode), 레지스터 번호를 인코딩하는 적은 수의 포멧이 있다.

- 규칙성이 있다.

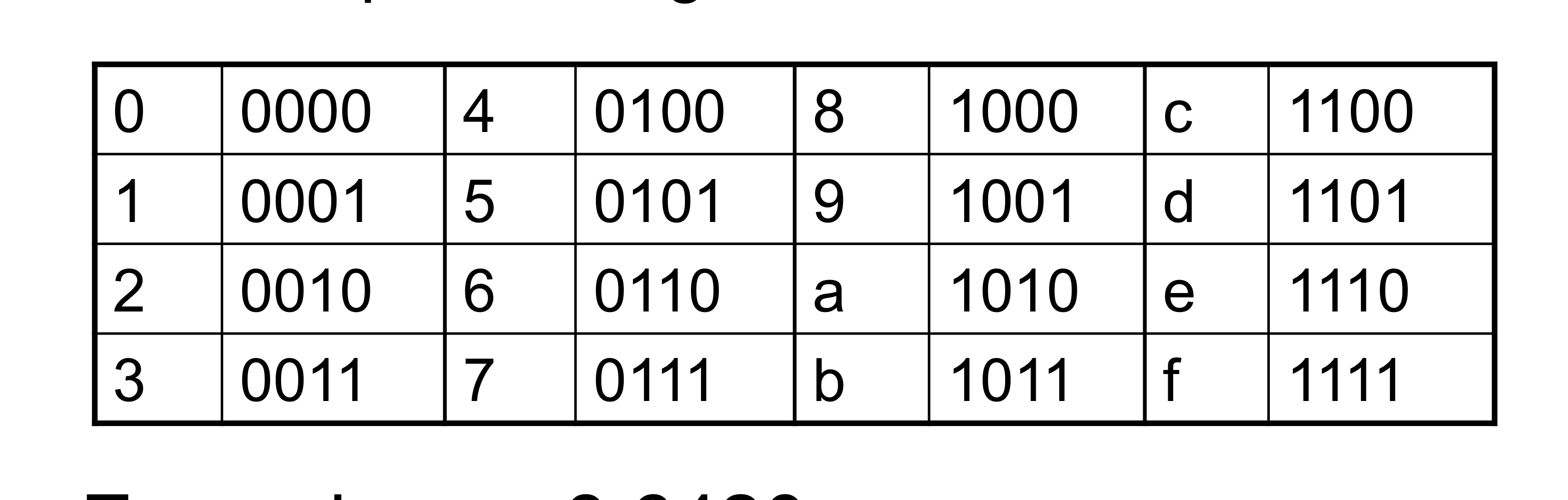

Hexadecimal

- 비트 문자열의 간결한 표현에 적합하다.

- 4비트씩 묶어서 하나의 16진수를 표현한다.

- Example

- eca8 6420

- = 1110 1100 1010 10000 0110 0100 0010 0000

LEGv8 R-format Instruction

- R(egister)-Format

- 피연산자로는 레지스터만 존재한다.

- 32개의 레지스터를 구분하기 위한 5비트.

- 명령어 필드

- opcode : 명령어 코드

- Rm : 두번 째 레지스터 소스 연산자

- shamt : 시프트를 할 양

- Rn : 첫번 째 레지스터 소스 연산자

- Rd : 명령어 실행 결과가 저장될 레지스터(destination)

- Example

LEGv8 D-format Instructions

- D(ata)-format Instruction

- Load / Store Instruction

- Rn : 베이스 레지스터

- address : 베이스 레지스터의 내용(주소값)으로 부터의 상수 오프셋

- Rt : Destination (load) 혹은 source (store) 레지스터

디자인 원칙 3 : Good Design demands Good compromises ; 좋은 디자인은 좋은 타협을 요구한다.

- 다른 형식의 포멧은 디코딩을 복잡하게 하지만, 32bit 명령어의 일관성을 가질 수 있따.

- 포멧을 가능한 비슷하게 유지할 수 있다.

LEGv8 I-format Instruction

- I(mediate)-format

'🖥CS > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터구조] 1. Computer Abstractionsand Technology (0) | 2024.09.11 |

|---|