Computer Revolution

컴퓨터 기술의 발전의 이해의 중요한 요소중 하나는 무어의 법칙(Moore's Law)였다.

무어의 법칙 : 마이크로 칩의 용량이 2(1.5)년 마다 2배 증가하고 가격은 반으로 줄어든다.

-> 최근에는 물리적인 한계로 인해 무어의 법칙이 잘 맞지는 않는다.

-> 하드웨어의 발전보다는 코어를 여러개 사용하는 Parallel 방식으로 진행된다.

이러한 기술적 발전은

- 자동차에 컴퓨터를 이식하고,

- 스마트폰의 시대를 만들었고

- 휴먼 게놈 프로젝트를 가능하게 하였고

- World Wide Web, Search Engine 등 다양한 기술을 가능하게 만들었다.

Classes Of Computer

- Personal Computers

- 상용적이고, 다양한 소프트웨어가 있다.

- 비용과 성능 사이의 trade off가 있다.

- Server Computer

- 네트워크를 기반으로 하고 있음

- 가용성이 높고, 성능, 신뢰성이 높다.

- 작은 서버부터 빌딩 사이즈의 서버까지 있다.

- Super Computer

- 최고 사양의 계산 성능을 보여줌

- 최고의 능력을 보여주지만, 컴퓨터 시장의 아주 작은 부분만을 차지하고 있다.

- Embedded Computers

- 시스템들의 요소이지만 눈에 띄지 않는다.

- 파워, 성능, 비용 측면에서 엄격한 제한 조건이 있다.

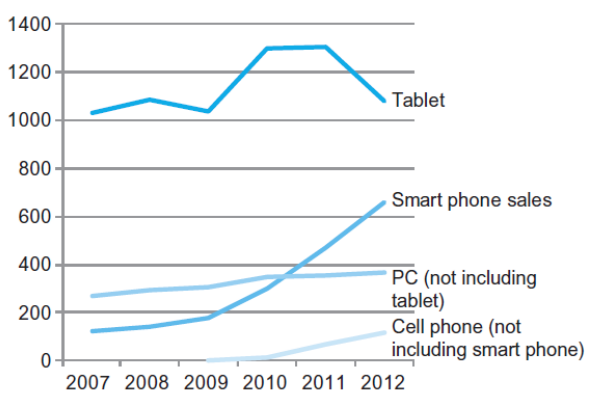

The PostPC Era

PC이외에도 다양한 기기들이 존재한다.

- Personal Mobile Device(PMD)

- 베터리로 작동함.

- 인터넷에 연결이 가능함

- 수백 달러정도의 가격대를 형성

- 스마트폰, 태블릿등이 속한다.

- Cloud Computing

- 클라우드 컴퓨팅은 세가지 서비스로 분류된다.

- IaaS : Infrastructure as a Service (하드웨어 자원 제공)

- PaaS : Platform as a Service (시스템 + 플랫폼(운영체제) 제공)

- SaaS : Software as a Service (소프트웨어(한글,PPT....)제공)

- 클라우드 컴퓨팅은 세가지 서비스로 분류된다.

What WE Will Learn?

- 어떻게 프로그램들이 Machine Language로 번역되는가?

- CPU가 알아먹을 수 있는 언어로 번역한다.

- CISK(Complex Instruction Set Computer) - X86 (Intel, AMD)

- RISK(Reduced Instruction Set Computer) - ARM

- -> 두 진영의 어셈블리어는 서로 다르다!

- CPU가 알아먹을 수 있는 언어로 번역한다.

- 그리고 하드웨어는 그것을 어떻게 실행하는가?

- 하드웨어/소프트웨어 인터페이스

- 프로그램의 성능을 좌우하는 요소는 무엇인가?

- 그렇다면 어떻게 성능을 향상시킬 수 있는가?

- 하드웨어 디자이너는 어떻게 성능을 향상시킬 수 있는가?

- 병렬 프로세싱이란 무엇인가?

Understanding Performance

- 알고리즘

- 알고리즘은 실행되는 명령어의 수를 결정한다 (by 소스코드)

- ex) 정렬이라는 결과는 같지만 동작 방식이 서로 다른 여러 정렬 알고리즘들.

- Programming Language, Compiler, Architecture

- 컴파일하여 Assembly 언어로 바꾸었을 때 명령어의 수를 결정함

- Processor and memory System

- 명령들이 얼마나 빠르게 실행될 수 있는 지를 좌우함

- ex) 캐시를 사용

- I/O System , OS

- I/O작업이 얼마나 빠르게 동작하는지를 좌우함.

성능을 위한 8가지 아이디어

- Design for Moore's Law

- 무어의 법칙에 따라 하드웨어 성능 향상을 감안하여 개발하기

- Use Abstraction to Simplify Design

- 하드웨어의 구현은 신경쓰지 않고 디자인을 심플하게

- Make the Common case Fast

- 100번중 99번 더하기가 동작한다면 더하기 성능에 집중하기

- Performance via Parallelism

- 병렬(코어 여러개)를 사용하여 성능 향상

- Performance via Pipelining

- Performance via prediction

- Hierarchy of memories

- Dependability via redundancy

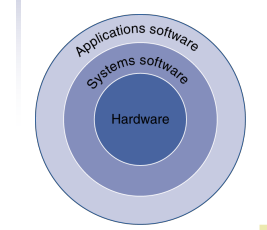

Below Our Program

- Application software

- high-level language로 작성되어 있다.

- System software

- 컴파일러 : High Level Language를 machine code로 변환시켜줌

- 이때 CPU에 dependent하게 동작해야함.

- Operating System(운영체제) : 서비스 코드

- Input/Output을 다룸

- 메모리와 저장공간을 관리함

- 스케줄링과, 자원 분할을 관리

- 컴파일러 : High Level Language를 machine code로 변환시켜줌

- Hardware

- 프로세서, 메모리, I/O 컨트롤러

하드웨어는 시스템 소프트웨어(운영체제)가 직접 제어

어플리케이션은 시스템 콜을 통해 시스템 소프트웨어를 거쳐 하드웨어에 접근(직접 제어x)

어플리케이션 -> 라이브러리 -> 시스템콜 -> 시스템 소프트웨어 -> 하드웨어

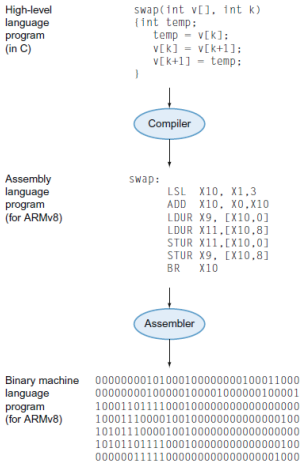

Levels Of Program Code

- High Level Language

- 도메인과 가까운 추상 레벨의 언어이다.

- 생산성과 이식성 향상을 제공한다.

- Assembly Language

- 명령어의 텍스트 표현.

- CPU에 종속적이다.

- Hardware Representation

- 바이너리 숫자들로 구성되어 있다. (비트; 0과 1)

- CPU는 한 줄씩 읽으면서 실행해나간다. (32비트 프로세서라면 32개씩 읽어가며)

Abstractions

추상화를 통해서 lower-level의 디테일들은 숨길 수 있게 도와준다.

- Instruction Set Architecture (ISA)

- 하드웨어와 소프트웨어의 인터페이스이다.

- x86용 ISA, ARM용 ISA등 서로 다른 ISA들이 존재한다.

- Application Binary Interface (ABI)

- ABI = CPU(ISA) + 운영체제

- ABI가 같다면 바이너리 코드 또한 동일하다.

Response Time and Throughput

- Response Time (응답 시간)

- 프로그램이 시작되어 끝날 때까지 걸린 시간을 의미한다.

- Response Time =

- CPU Queue에 들어오는 시간 (I/O Blocking 포함)

- CPU Queue에서 대기하는 시간 (by Scheduler)

- CPU TIME (실제 CPU에서 동작하는 시간)

- Throughput

- 유닛 타임당 소화할 수 있는 테스크(프로세스)의 수를 의미한다.

- 더 빠른 프로세서를 사용하거나 더 많은 프로세서를 사용한다면??

- Response Time과 Throughput또한 향상될 것이다.

- 성능에서 Response Time과 Throughput을 고려할 때는 스케줄러와 밀접한 관련이 있다.

Relative Performance

성능은 "1/Execution Time"으로 정의할 수 있다.

Measuring Execution Time

- Elapsed Time

- 모든 요소를 포함하는 총 반환 시간이다.

- 프로세싱, I/O, OS 오버헤드, idle time 모두를 포함한다.

- CPU Time

- 주어진 job을 프로세싱하는데 걸리는 시간이다.

- I/O와 같은 다른 작업들은 배제하고, CPU에서 돌아간 시간만을 생각한다.

- User CPU Time 과 System CPU Time으로 이루어져 있다.

CPU Time

- CPU Time =

- CPU Clock Cycles (프로세스에서 명령어들이 총 몇 사이클을 사용했는가)

- X Clock Cycle Time ( 한 사이클이 돌아가는 데 얼마나 소요되는가)

- = CPU Clock Cycles / Clock Rate

성능은

- clock Cycle의 수를 줄이거나 (ISA에 의해 좌우됨. 같은 ISA라도 하드웨어 구조 설계에 따라 달라짐)

- Clock Rate를 높이거나

를 통해 향상 시킬 수 있다.

Instruction Count and CPI

- CPI(Cycle Per Instruction)

- 인스트럭션 하나당 걸리는 사이클의 수

- 모든 ISA의 명령어들이 소요하는 사이클 수의 평균으로 계산 가능하지만 이 경우에는 부정확할 수 있음

- 프로그램의 명령어 수

- 프로그램(알고리즘에 따라 명령어의 수가 달라짐)

- ISA (ISA에 따라 명령어 수가 다름)

- 컴파일러(컴파일러의 최적화에 따라 수가 달라짐)

Performance 요약

- 성능을 결정하는 요소들

- 알고리즘 : IC(Instruction Count) , CPI(Cycle Per Instruction)

- 프로그래밍 언어 : IC(Instruction Count) , CPI(Cycle Per Instruction)

- 컴파일러 : IC(Instruction Count) , CPI(Cycle Per Instruction)

- ISA : IC(Instruction Count) , CPI(Cycle Per Instruction)

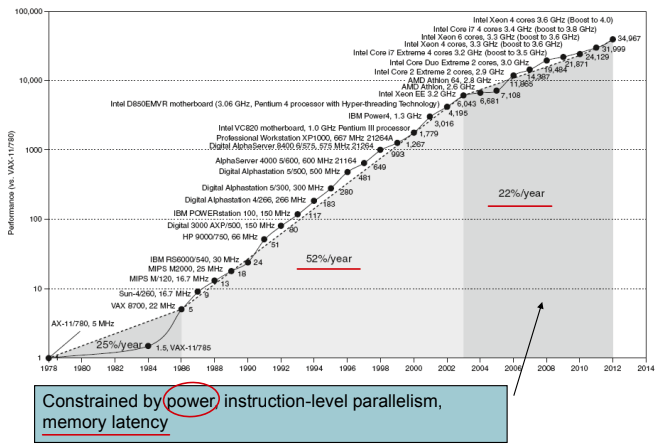

Power Trends

Power = Capacity load x Voltage^2 x Frequency

-> Frequency는 집적도가 높아짐에 따라 같이 증가함 (무어의 법칙)

-> Voltage는 공정의 발전으로 적은 볼티지로도 가동할 수 있게됨.

=> Frequency가 1000배 증가하고, Voltage가 5V에서 1V로 감소한다면 Power는 30배 증가하게 된다.

-> 이제는 Clock Rate를 증가시키기 보다는 Power을 줄이고, 코어의 수를 늘리는 방향으로 발전하고 있다.

Uniprocessor Performance

단일 프로세서 만으로는 성능 향상에 한계점이 있다.

Multiprocessors

- 멀티 프로세서는 칩 하나당 하나 이상의 프로세서를 사용한다.

- 비교

- Uniprocessor

- 하드웨어(코어 하나)는 파이프라인을 통해서 여러개의 Instruction을 한번에 실행

- 프로그래머에게 숨겨져 있어 관여 할 필요가 없다.

- Multiprocessor

- 병렬 프로그래밍을 필요로 한다.

- 로드 밸런싱 필요

- 스레드들간의 커뮤니케이션과 동기화를 고려해야 함.

- Uniprocessor

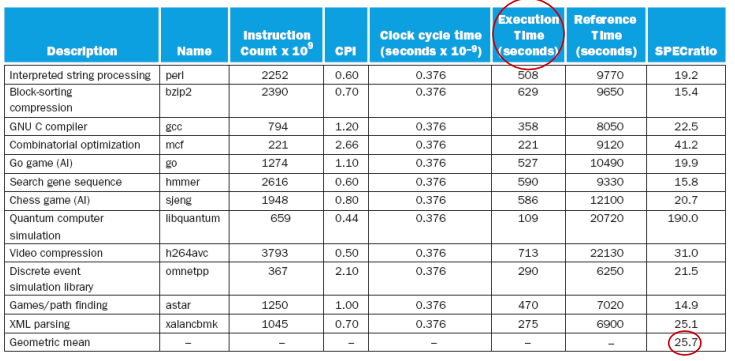

SPEC CPU Benchmark

- 성능을 측정하기 위한 프로그램

- Standard Performance Evaluation Corp(SPEC)에서 I/O, CPU, Web등을 위한 벤치마크를 개발함.

- SPEC CPU2006

- 프로그램을 실행시간을 측정

- I/O는 배제하여 CPU 성능에만 집중

- Normalize relative to reference machine

- Summarize as geometric mean of performance ratios

CINT2006 : 12개 정도의 Integer에 대한 계산을 수행하고 평균을 계산

CFP2006 : 19정도의 Floating-Point 계산을 수행하고 평균을 계산

SPEC Power Benchmark

서버의 전력 소비와 성능

**ssj : Server-Side Java**

- Performance (성능) : ssj_ops / sec

- Power (전력) : Joules / sec

위 표에서 Target Load가 0%일 때 파워 소모량이 0이 아님에 유의해야 한다!

PITFALL : Amdahl's Law

- 암달의 법칙

- 시스템의 한 가지 요소를 개선한다고 해서 전체 성능이 비례해서 향상되는 것은 아니다.

- 시스템의 전체 성능은 개선할 수 없는 부분에 의해 제한된다는 원칙이다.

- 예시) 어떤 100s의 프로그램중 곱셈이 80s를 차지한다고 가정하자

- 곱셈의 성능을 향상시켜서 총 프로그램의 성능을 5배 향상시킬 수 있을까?

- 80/n + 20 == 20을 만족하는 n값은 존재하지 않는다.

- 따라서 5배의 성능 향상은 불가능하다.

- 예시) 어떤 100s의 프로그램중 곱셈이 80s를 차지한다고 가정하자

PITFALL : MIPS as a Performance Matric

- MIPS : Millions of Instruction Per Second

- MIPS는....

- 컴퓨터에서 사용하는 ISA의 다름을 고려하지 않음

- instruction 간의 서로 다른 복잡도는 고려하지 않음

- MIPS는 ISA를 고려하지 않음 지표임에 유의해야 한다.

- MIPS는....

'🖥CS > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터구조] 2. Instructions : Language of the Computer (0) | 2024.09.18 |

|---|